# Integration of 1024 InGaAsP/InP Optoelectronic Bistable Switches

KENICHI MATSUDA, KYOKO TAKIMOTO, DOO-HWAN LEE, AND JUN SHIBATA

Abstract—We have proposed and fabricated a photonic parallel memory (PPM) which is an array of 32  $\times$  32 optoelectronic bistable switches. The switch consists of a heterojunction phototransistor (HPT) and a light-emitting diode (LED), and optical positive feedback from LED to HPT is the cause of bistability. PPM can be written in and read out with 1-kb parallel optical signals. PPM has been fabricated successfully and memory operation has been demonstrated as expected. Dissipation current for a single switch and the input optical power necessary to turn on the switch were 600  $\mu A$  and 20  $\mu W$ , respectively. Light pulse with a width of 5 ns was able to turn on the switch and product of turn-on power and pulsewidth for short pulse region was 1.5 pJ.

#### I. Introduction

THERE has been much interest in parallel processing **1** architecture, especially in optical parallel processing since light has the inherent advantage of parallelism and interconnectivity [1]. A large optical array processor with modest switching speeds per device may be able to handle a much larger number of bits per second than the fastest serial processor available today. One way to realize the optical array processor is integration of "pure" optical switches which do not need carrier injection. The pure optical switches have a capability of high-speed switching [2], and an array consisting of over  $100 \times 100$  devices has been demonstrated [3]. They need, however, high input optical power and have no gain for optical signals. Another way is integration of optoelectronic bistable switches which can operate with lower optical power and amplify optical signals, though the speed is limited by the lifetime of injected carrier.

In regard to a single switch, several kinds of optoelectronic bistable switches have already been proposed and demonstrated, such as a light-emitting device with p-n-p-n or p-n-n structure [4], [5], an integrated device of heterojunction phototransistor (HPT) and a light-emitting diode (LED) [6], [7], and a self-electrooptic effect device (SEED) [8]. In this paper we demonstrate an array of 32 × 32 optoelectronic bistable switches consisting of HPT and LED. In the switch, HPT and LED are connected electrically in series and light emitted from LED is fed

Manuscript received September 5, 1989; revised February 7, 1990. The review of this paper was arranged by Associate Editor G. Craford.

The authors are with the Opto-Electronics Research Laboratory, Matsushita Electric Industrial Co., Ltd., 3-15 Yagumo-Nakamachi, Moriguchi, Osaka 570, Japan.

IEEE Log Number 9035770.

back to HPT. This optical positive feedback is the cause of bistability [9]. The switch has advantages of inherent gain and unidirectionality for optical signals [7] as well as simple structure suitable for large-scale integration. The array can operate as a 1-kb memory with a function of optical parallel processing. This photonic parallel memory (PPM) can be written in and read out with 1-kb parallel optical signals. It can operate also as a 1-kb parallel or gate when different signals are written in either sequentially or simultaneously.

#### II. STRUCTURE AND FABRICATION

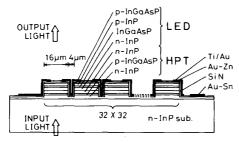

The structure of PPM is shown in Fig. 1. It contains 32 × 32 mesas isolated by etched grooves. The groove has a width of 4  $\mu$ m and a depth of 5  $\mu$ m, and the remaining mesa has an area of  $16 \times 16 \,\mu\text{m}^2$ . Each mesa is a bistable switch consisting of seven layers which are an n-InP emitter ( $\sim 4~\mu m$ ,  $5~\times 10^{17}~cm^{-3}$ ), a p-InGaAsP base (0.25  $\mu m$ ,  $1~\times 10^{17}~cm^{-3}$ , bandgap wavelength  $\lambda_g = 1.3~\mu m$ ), an n-InP collector (0.9  $\mu m$ ,  $1~\times 10^{17}~cm^{-3}$ ), an n-InP clad (0.9  $\mu m$ ,  $1~\times 10^{18}~cm^{-3}$ ), an InGaAsP active layer (0.3  $\mu$ m, undoped,  $\lambda_g = 1.3 \mu$ m), a p-InP clad (1.0  $\mu$ m,  $5 \times 10^{17}$  cm<sup>-3</sup>), and a p-InGaAsP cap (0.1  $\mu$ m, 2  $\times$  10<sup>18</sup> cm<sup>-3</sup>,  $\lambda_g = 1.1 \mu$ m). The first three and the remaining four layers constitute HPT and LED, respectively. All the switches are wired in parallel with a Ti/Au interconnection metal. The Ti/Au plays also a role of optical isolation for the switches since it surrounds all the sidewalls of the mesas. As shown in Fig. 1, input light is incident upon HPT through the substrate and output light is emitted upward from the LED. This "passing-through" configuration can be attained by the fact that the substrate and the epitaxial layers other than the base of HPT and the active layer of LED are transparent to light with a wavelength of 1.3 µm which is used as input and output signals.

To fabricate PPM, the seven layers mentioned above were first grown on an  $n^+$ -InP substrate by liquid phase epitaxy (LPE). Then SiN (2000 Å) and Ti (4000 Å) were deposited and patterned with reactive ion etching (RIE) using CF<sub>4</sub> and CCl<sub>4</sub>, respectively. They were etched using photoresist as a mask and used as a mask for etching epitaxial layers to form the grooves. The epitaxial layers were etched with RIE using a mixture of Br<sub>2</sub> and Ar gases [10]. After mesa formation, Au–Zn ring anodes were evaporated on the tops of the mesas and Au–Sn cathodes

0018-9383/90/0700-1630\$01.00 © 1990 IEEE

Fig. 1. Schematic cross section of a photonic parallel memory. Each mesa consisting of a heterojunction phototransistor (HPT) and a light-emitting diode (LED) is an optoelectronic bistable switch.

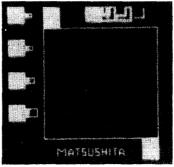

were outside the mesas where the emitter was exposed. A scanning electron microscope (SEM) photograph of cleaved mesas with ring anodes is shown in Fig. 2. After contact evaporation, a Ti/Au interconnection metal was evaporated on a SiN passivation film to connect all of the anodes. Finally, the back surface of the wafer was polished so that input light could be incident upon the bottom of the switch. The photomicrograph of a fabricated chip is shown in Fig. 3. The chip has an area of  $1.0 \times 1.0 \, \mathrm{mm^2}$  including bonding pads and single switches for testing, while the active area for integration is  $640 \times 640 \, \mathrm{\mu m^2}$ .

#### III. CHARACTERISTICS OF A SINGLE SWITCH

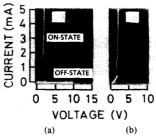

Characteristics of a single switch have first been measured. As shown in Fig. 4(a), a thyristor-like voltagecurrent curve was observed unless input light was incident. In this curve, "on-state" and "off-state" are clearly distinguished. Output light was emitted from the top of the switch in the on-state which could be observed through an infrared video camera. Then the light emitted from a  $1.3-\mu m$  laser diode was incident upon the bottom of the switch through a single-mode fiber with a focusing lens. As input optical power was increased, the breakdown voltage was decreased and a diode-like curve shown in Fig. 4(b) was observed when the input power measured at the fiber end was 175  $\mu$ W. In case of operating it with a constant bias voltage, the switch is turned on before this condition. In other words, the input optical power necessary to turn on the switch (turn-on power) depends on the bias voltage and the maximum value is equal to the input optical power necessary to obtain a diode-like curve.

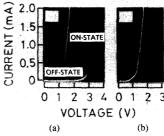

Considering operation of PPM, it is desirable to decrease both turn-on power and dissipation current in the on-state. The minimum current to maintain the on-state (holding current) can be found from voltage-current characteristics and is 1.6 mA for the switch shown in Fig. 4. The characteristics for another switch with a holding current of 600  $\mu$ A are shown in Fig. 5. The input optical power necessary to obtain a diode-like curve has also been reduced to 20  $\mu$ W. For this switch, the collector of HPT was changed to be InGaAsP and the base was made to be thinner ( $\sim 0.15~\mu$ m). As can be seen in Fig. 5(a), the breakdown voltage without input light is also reduced

Fig. 2. SEM photograph of cleaved mesas with ring anodes on a PPM chip. The grooves are etched with RIE using a mixture of Br<sub>2</sub> and Ar gases.

Fig. 3. Photomicrograph of a fabricated PPM chip. The chip has an area of  $1.0 \times 1.0$  mm<sup>2</sup> including bonding pads and single switches for testing. The active area for integration is  $640 \times 640 \mu m^2$ .

Fig. 4. Voltage-current characteristics of a single switch with an InP collector and a thick (  $\sim 0.25~\mu m$ ) base: (a) without input light and (b) with an input light of 175  $\mu W$ .

Fig. 5. Voltage-current characteristics of a single switch with a quarternary collector and a thin (  $\sim 0.15~\mu m$ ) base: (a) without input light and (b) with input light of 20  $\mu W$ .

since breakdown caused by punchthrough occurs at lower bias voltage for HPT with a thinner base.

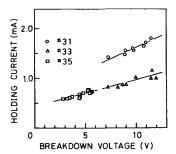

To separate the cause for reduction of holding current, the relations between the breakdown voltage without input light and the holding current have been measured for three types of switches which were selected from three different wafers. They were the wafer with an InP collector and a thick ( $\sim 0.25 \mu m$ ) base (#31), with a quarternary collector and a thick base (#33), and with a quarternary collector and a thin ( $\sim 0.15 \mu m$ ) base (#35). The results are shown in Fig. 6. The breakdown voltage depends on the thickness of the base layer and the various values of breakdown voltage observed in switches on the same wafer are attributed to nonuniformity of layer thickness. The switches with a quarternary collector have smaller holding current than those with an InP collector, and the switches with lower breakdown voltage, which corresponds to thinner base, have smaller holding current. The mechanism which determines holding current will be discussed later.

#### IV. CIRCUIT OPERATION

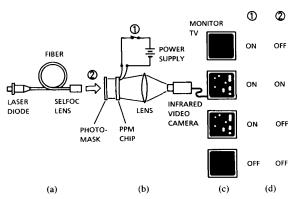

The experimental setup for operating PPM is shown in Fig. 7 together with a schematic diagram of memory operation. The power supply voltage ranging from 1.6 to 2.2 V is first applied to all the switches without input light. They are in the off-state and no light emission is observed. Then the light is incident to selected switches, which are turned on and emit output light. Selection of the switch is done by setting a photomask between the light source and the chip. The on-state is maintained after removing the input light and the selected switches keep emitting light. All the switches are turned off by making the supply voltage zero. An example of a memorized pattern on a PPM chip observed with an infrared video camera is shown in Fig. 8. A Chinese character is displayed with 56 selected switches which are turned on and emit light.

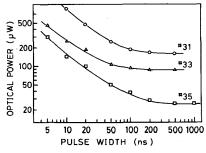

To evaluate the processing rate of PPM, turn-on and turn-off speeds were measured as follows. For the turnon speed, a light pulse with varying pulsewidth was incident upon one of the integrated switches and turn-on power was measured. The results are shown in Fig. 9. The measurement was done for three types of PPM chips on wafers #31, #33, and #35 mentioned in the previous section. The light pulse with a width of 5 ns can turn on the switches on wafers #33 and #35 though the turn-on power is increased as the pulsewidth is decreased. The product of the turn-on power and pulsewidth for the shortpulse region is calculated to be 1.5 pJ for switch on water #35. The results shown in Fig. 9 were obtained using a supply voltage of 1.9 V which is sufficiently larger than the minimum voltage to maintain the on-state (holding voltage). The turn-on power depends slightly on the supply voltage when the difference between the supply voltage and the holding voltage is larger than 0.2 V. When the difference is less than 0.2 V, the turn-on power rapidly increases as the supply voltage approaches the holding voltage.

Fig. 6. Relations between breakdown voltage without input light and holding current. The switches are selected from three different wafers: with an InP collector and a thick base (#31), with a quarternary collector and a thick base (#33), and with a quarternary collector and a thin base (#35).

Fig. 7. Experimental setup for operating a PPM chip together with the schematic diagram of memory operation: (a) initial state, (b) write-in operation, (c) memory operation, and (d) reset.

Fig. 8. Infrared image of a PPM chip in memory operation. A Chinese character meaning "a pine tree" is memorized and read out.

Fig. 9. Relations between pulsewidth of input light and turn-on power for single switches integrated in PPM chips on wafers #31, #33, and #35.

To measure the turn-off speed, the switches were first turned on and then the supply voltage was reduced to zero during a short period. The length of the period necessary to turn off the switches (turn-off time) was 26, 44, and 285 ns for wafers #31, #33, and #35, respectively, when the supply voltage for the on-state was 1.9 V. The turn-off time strongly depends on the supply voltage for the on-state and a value lower than 5 ns can be obtained for all the wafers in case of setting the supply voltage to the holding voltage. When the supply voltage is 0.2 V larger than the holding voltage, the turn-off time is about 30 ns. Therefore, the expected cycle time for turn-on and turn-off is 30-40 ns although the speed for cycle operation has not been measured.

## V. DISCUSSION

The dissipation current  $(I_d)$ , the output optical power  $(P_{out})$ , and the input optical power  $(P_{in})$  of the switch are related by following equations:

$$P_{\text{out}} = \eta_e I_d \tag{1}$$

$$I_d = G(kP_{\text{out}} + P_{\text{in}}) \tag{2}$$

where  $\eta_e$  is the efficiency of LED in watts per ampere, G is the optical gain of HPT in amperes per watt, and k is the ratio of the feedback optical power to the output optical power. In general, G is increased as  $I_d$  increases [11], while  $\eta_e$  and k are considered to be approximately constant. The measured value of  $\eta_e$  is about  $1 \times 10^{-2}$  W/A, and k is ideally equal to 1, since downward light emitted from the LED has the same power as upward light. In case of  $P_{\rm in}=0$ , the trivial solution of (1) and (2) is  $I_d=0$ , which denotes the off-state. The other solution corresponding to the on-state is  $G(I_d)=(k \eta_e)^{-1}$ . Therefore, it is important to fabricate HPT with high optical gain in low current region in order to obtain the switch with low dissipation current. As can be seen from (2), such HPT can also reduce the turn-on power.

The above discussion can qualitatively explain the experimental results shown in Fig. 6. The optical gain of HPT is the product of optical absorption efficiency ( $\eta_a$ ) and current gain  $(\beta)$ . The switches with a quarternary collector have smaller holding current than those with an InP collector because the quarternary collector increases  $\eta_a$ . The switches with a thinner base have smaller holding current since it increases  $\beta$ . The turn-on power is also reduced by using a quarternary collector or a thin base, which is demonstrated in Fig. 9. In this figure, the turnon power for the long-pulse region coincides with that in dc mode operation. The turn-on power for the switch with a thin base (#35) approaches that for the switch with a thick base (#33) in the short-pulse region because the current gain of HPT in the high-frequency region is limited by the gain-bandwidth product. The gain-bandwidth product has little relation to base thickness since it is not limited by base transit time but by the CR time constant.

Another important result obtained from (2) is that the turn-on power is less than  $kP_{\text{out}}$  in the on-state. This is

because  $P_{\rm in}$  equal to  $I_d/G$  in the on-state is enough for turning on the switch and  $I_d$  is equal to  $GkP_{\rm out}$  in case of  $P_{\rm in}=0$ . Therefore, the switch has optical gain larger than unity whenever it can be turned on if k is equal to 1. In fact, however, considering the case of the switch shown in Fig. 4, the output power is approximately  $20~\mu{\rm W}$  when it is operated with a current of 2 mA, while the turn-on power is  $175~\mu{\rm W}$ . This discrepancy may be attributed to the fact that k is much larger than unity because the output light is shaded by contact and interconnection metals although the feedback light is detected by the base of the HPT without optical loss. The output power increases as the dissipation current is increased and the switch shown in Fig. 5 has an optical gain of about 4.6 when it is operated with a current of 10 mA.

# VI. Conclusions

1-kb PPM which is an array of  $32 \times 32$  optoelectronic bistable switches has been fabricated successfully. The memory operation of PPM with functions of optical write-in and readout has been demonstrated as expected. The minimum current to maintain the on-state and the input optical power necessary to turn on the switch were 1.6 mA and 175  $\mu$ W, respectively, for the switch with an InP collector and a thick ( $\sim 0.25~\mu$ m) base. They were improved to  $600~\mu$ A and  $20~\mu$ W by using a quarternary collector and a thin ( $\sim 0.15~\mu$ m) base. The light pulse with a width of 5 ns was able to turn on the switch and the product of turn-on power and pulsewidth for a short-pulse region was 1.5 pJ.

### ACKNOWLEDGMENT

The authors wish to thank Prof. A. Sasaki for suggesting the basic idea of the optoelectronic bistable switch. They are also indebted to T. Kajiwara, K. Ohnaka, and M. Kubo for their encouragement and fruitful discussions.

# REFERENCES

- A. Huang, "Architectural considerations involved in the design of an optical digital computer," *Proc. IEEE*, vol. 72, pp. 780-786, Jul. 1984.

- [2] D. Hulin, A. Mysyrowicz, A. Antonetti, A. Migus, W. T. Masselink, H. Morkoç, H. M. Gibbs, and N. Peyghambarian, "Ultrafast all-optical gate with subpicosecond on and off response time," *Appl. Phys. Lett.*, vol. 49, pp. 749-751, Sept. 1986.

- [3] T. Venkatesan, B. Wilkens, Y. H. Lee, M. Warren, G. Olbright, H. M. Gibbs, N. Peyghambarian, J. S. Smith, and A. Yariv, "Fabrication of arrays of GaAs optical bistable devices," *Appl. Phys. Lett.*, vol. 48, pp. 145-147, Jan. 1986.

- [4] Zh. I. Alferov, V. I. Korol'kov, V. G. Nikitin, and D. N. Tret'yakov, "Solid-state infrared radiation converter," Sov. Phys.—Semicond., vol. 5, pp. 1314-1317, Feb. 1972.

- [5] G. W. Taylor, J. G. Simmons, A. Y. Cho, and R. S. Mand, "A new double heterostructure optoelectronic switching device using molecular beam epitaxy," J. Appl. Phys., vol. 59, pp. 596-600, Jan. 1986.

- [6] A. Sasaki, K. Matsuda, Y. Kimura, and S. Fujita, "High-current InGaAsP-InP phototransistors and some monolithic optical devices," *IEEE Trans. Electron Devices*, vol. ED-29, pp. 1382-1388, Sept. 1982.

- [7] A. Sasaki, M. Taneya, H. Yano, and S. Fujita, "Optoelectronic integrated device with light amplification and optical bistability," *IEEE Trans. Electron Devices*, vol. ED-31, pp. 805-811, June 1984.

- [8] D. A. B. Miller, D. S. Chemla, T. C. Damen, T. H. Wood, C. A. Burrus, Jr., A. C. Gossard, and W. Wiegmann, "The quantum well self-electrooptic effect device: optoelectronic bistability and oscillation, and self-linearized modulation," *IEEE J. Quantum Electron.*, vol. QE-21, pp. 1462-1476, Sept. 1985.

[9] Y. Ogawa, H. Itoh, and H. Inaba, "New bistable optical device using

- [9] Y. Ogawa, H. Itoh, and H. Inaba, "New bistable optical device using semiconductor laser diode," *Japan J. Appl. Phys.*, vol. 20, pp. L646– L648, Sept. 1981.

- [10] K. Takimoto, K. Ohnaka, and J. Shibata, "Reactive ion etching of lnP with Br<sub>2</sub>-containing gases to produce smooth, vertical walls: Fabrication of etched-faceted lasers," Appl. Phys. Lett., vol. 54, pp. 1947-1949, May 1989.

- [11] A. Sasaki and M. Kuzuhara, "InGaAsP/InP heterojunction phototransistors and light amplifiers," *Japan J. Appl. Phys.*, vol. 20, pp. L283-L286, Apr. 1981.

Kenichi Matsuda was born in Osaka, Japan, on November 5, 1957. He received the B.S. and M.E. degrees in electrical engineering from Kyoto University, Kyoto, Japan, in 1980 and 1982, respectively.

In 1982, he joined Matsushita Electric Industrial Co., Ltd., Osaka, Japan, and has been working on the development of InP-based optoelectronic integrated circuits.

Mr. Matsuda is a member of the Institute of Electronics, Information and Communication En-

gineers and the Japan Society of Applied Physics.

Kyoko Takimoto received the B.S. and M.S. degrees in physics from Kobe University, Kobe, Japan, in 1981 and 1983, respectively.

In 1983, she joined Matsushita Electric Industrial Co., Ltd., Osaka,

In 1983, she joined Matsushita Electric Industrial Co., Ltd., Osaka, Japan. Since 1987, she has been working on dry-etching technologies for InP-based optoelectronic integrated circuits.

Ms. Takimoto is a member of the Japan Society of Applied Physics.

**Doo-Hwan Lee** was born in Seoul, Korea, on October 7, 1957. He received the B.S. degree in electronic engineering from Yonsei University, Seoul, Korea, in 1980, and the M.E. and Ph.D. degrees in electrical engineering from the University of Florida, Gainesville, Florida, in 1986 and 1988, respectively.

In 1989, he joined Matsushita Electric Industrial Co., Ltd., Osaka, Japan, and has been working on the development of InP-based optoelectronic integrated circuits.

Dr. Lee is a member of the Electrochemical Society.

gineers.

Jun Shibata was born in Tokyo, Japan, on October 27, 1948. He received the B.S. degree in electric engineering from Tokyo Electric Engineering College, Tokyo, Japan, in 1971. In 1971, he joined Matsushita Electric Indus-

In 1971, he joined Matsushita Electric Industrial Co., Ltd., Osaka, Japan, and engaged in the development of silicon VLSI. Since 1981, he has been working on the development of optoelectronic IC's using the InGaAsP/InP system.

Mr. Shibata is a member of the Institute of Electronics, Information and Communication En-